Building Bridges in Tirana

The 1st Sino-European Workshop on Computer Architecture R&D and RISC‑V

Makeljana Shkurti

Business Strategy

Makeljana leads business strategy at VRULL and chairs the RISC-V International AI & ML Market Development Committee. A frequent speaker on technology strategy, she connects the commercial reality of AI silicon with the ecosystem decisions that make it viable.

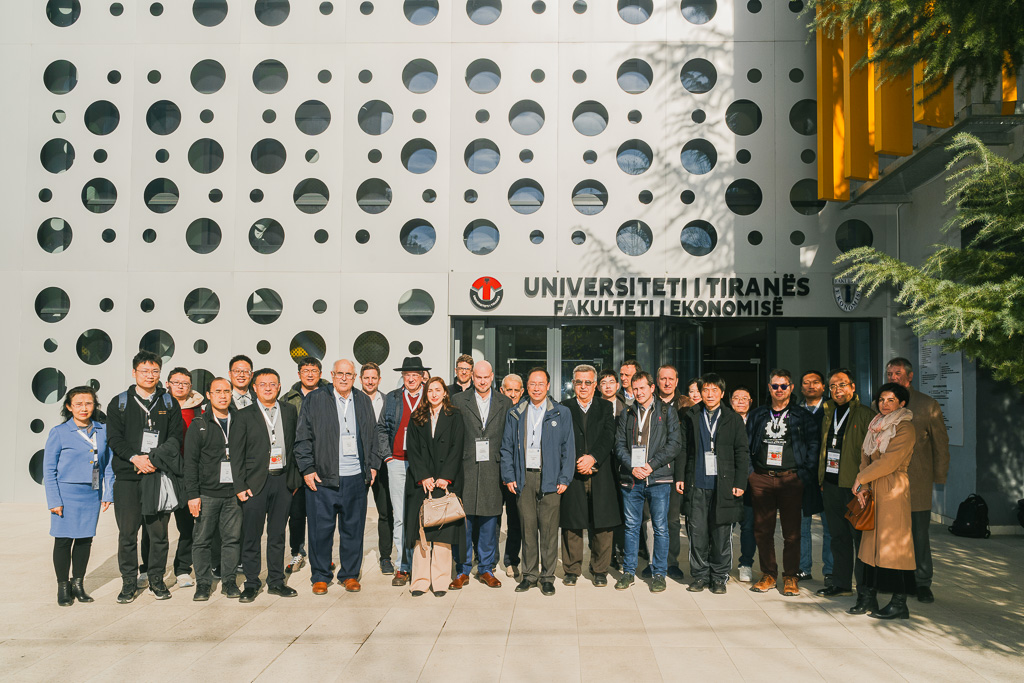

Tirana, Albania. January 2024. The first in a series of international RISC‑V collaboration workshops.

Open-source hardware has always promised something bigger than any single company or country could build alone. In January 2024, that promise took a concrete step forward in an unexpected place: Tirana, Albania, where researchers and engineers from China and Europe gathered for the first serious attempt to turn parallel RISC‑V development efforts into a coordinated, global R&D conversation.

The 1st Sino-European Workshop on Cooperation Opportunities in Computer Architecture R&D and RISC‑V was not a conference. No keynote stages, no vendor booths. It was a working workshop — deliberately small, deliberately focused — designed to answer a simple question: if the people building RISC‑V’s future in Beijing and in Basel, in Chongqing and in Munich, are working on overlapping problems, what happens when you put them in the same room?

The answer, over three days of sessions, shared meals, and late-evening discussions, was: a great deal.

Dr. Yungang Bao and BOSC

No figure better embodies the spirit of what this workshop was trying to build than Dr. Yungang Bao, Director of the Beijing Institute of Open Source Chip (BOSC) and one of the event’s co-organisers alongside VRULL’s Philipp Tomsich.

Dr. Bao has spent his career pursuing a vision that most of the semiconductor industry considered naive for a long time: that truly open processor architecture, developed transparently and collaboratively across institutions and borders, could outcompete closed proprietary alternatives — not despite its openness, but because of it. BOSC has become one of the most significant institutional forces behind RISC‑V’s development in China, driving open-source chip design, building the research community around it, and contributing to the international standardisation work that makes RISC‑V useful everywhere.

His presence in Tirana as co-organiser was not ceremonial. Dr. Bao arrived with an agenda: to meet with the European researchers and institutions whose work intersected most closely with BOSC’s, and to lay the groundwork for the kind of sustained collaboration that produces better standards, less duplicated effort, and ultimately better silicon for everyone.

Why collaboration is the point

RISC‑V is no longer an academic curiosity. It ships in data-centre accelerators, embedded microcontrollers, AI inference chips, and networking silicon. Toolchain support in GCC and LLVM has matured significantly. AI frameworks are being ported. The question is no longer whether RISC‑V will matter — it is whether the community building it will hang together well enough to realise its full potential.

Fragmentation is the real risk. RISC‑V’s modularity — the very thing that makes it adaptable — also creates the possibility of divergent extensions, incompatible toolchains, and ecosystems that can’t learn from each other. China and Europe are both investing heavily in RISC‑V R&D, and both are tackling the same hard problems: ISA extensions for AI workloads, compiler infrastructure, binary translation, software ecosystem bring-up. Without communication, that’s duplicated effort on a significant scale. With it, it’s a shared foundation that lifts everyone.

The Tirana workshop was built on the conviction that RISC‑V’s open model is only meaningful if the community that develops it is genuinely open — open to sharing work, aligning on standards, and treating the accumulated knowledge on both sides of the world as a common asset rather than a competitive advantage to be hoarded.

Three days that built something lasting

Day one established a shared picture: participants from China and Europe each presented the status and direction of their active research, giving the room a detailed view of what was being built and where. For many, it was the first time they had seen the full scope of what their counterparts were working on.

Day two sharpened into the hardest technical questions: RISC‑V and AI acceleration, binary translation, and the challenge of driving standardisation that actually works across geographies. These are not easy conversations — they require enough shared vocabulary and mutual trust to disagree productively. The groundwork laid on day one made it possible.

Day three moved into plenary: joint priorities for standardisation, frameworks for ongoing information exchange, and the outlines of future collaborative R&D. The goal was not to leave with a signed memorandum, but with enough shared clarity to make the next steps obvious.

Between sessions, Tirana itself contributed. Albania’s warmth and hospitality created an atmosphere that made honest conversation easy. Several of the most productive exchanges happened not in the session rooms but over dinner, in exactly the way the best workshops always work.

Albania as a participant, not just a host

One of the workshop’s most meaningful dimensions was the genuine engagement of Albanian institutions. The University of Tirana and Epoka University brought academic presence; the National Agency of Information Society (AKSHI) and the National Cyber Security Authority represented the policy side. The Polytechnic University of Tirana also participated. Delegates from the Chinese Embassy to Albania and AKSHI’s representative spoke at the opening, giving the event a diplomatic weight that reflected how seriously both sides took the occasion.

The room

The participant list reflected the full depth of what serious RISC‑V development requires. ISA designers, compiler engineers, hardware security researchers, AI framework developers, supercomputing specialists, and standards veterans — together. The range was deliberate. RISC‑V’s challenges don’t respect disciplinary boundaries, and neither did the guest list.

A beginning, not a summit

For VRULL, organising this workshop was an expression of something we see every day in our work: the best infrastructure for RISC‑V gets built by people who are talking to each other. Our work — compiler engineering, ISA design, full-stack platform bring-up — sits at the intersection where standards decisions meet production code. We know what happens when that chain is well-connected, and what is lost when it isn’t.

Bringing the Chinese and European research communities into sustained dialogue is part of the same work. Every hour of duplicated effort on a problem that could have been solved jointly is an hour not spent on the next hard thing. Every standard that gets designed without the full range of implementation experience behind it is a standard that will be revised.

The Tirana workshop was the first. We organised it with a simple hope: that it would become a tradition — a gathering that researchers and engineers working on computer architecture and open silicon would mark in their calendars, year after year.

The most important thing about this workshop is not what was decided in Tirana. It is what it started.

With thanks to all participants and supporters:

Dr. Yungang Bao (BOSC), Prof. Tao Xie (Peking University), Wei Wu (PLCT Lab / ISCAS), SOPHGO Technologies, Hyseim, PerfXLab Technologies, Prof. Xichuan Zhou (Chongqing University), Jiuyue Ma (BOSC), Xu An (BOSC), Christian Fabre (CEA-List), Prof. Frank Kagan Gurkaynak (ETH Zurich), Nick Kossifidis (ICS-FORTH), Dr. Daniel Mueller-Gritschneder (TU Munich), Markus Klemen (SBA Research), Bernard Dosti (University of Tirana), Betim Cico (Epoka University), Indrit Enesi (Polytechnic University of Tirana), Biwei Xie (ICT, CAS), Zihao Yu (ICT, CAS), Kaifan Wang (ICT, CAS), Siqi Zhao (Alibaba), Liuxi Yang (Sophgo), Xintong Wang (Sophgo), Weibing Wang (HySeim), Xiaolan Ma (HySeim), Xianyi Zhang (PerfXLab), and representatives from the Embassy of the P.R.C. to Albania, AKSHI, AKCESK, and the Albanian National Nuclear Agency.

Faleminderit.